## Thesis for the Degree of Doctor of Philosophy

## Effective SAT Solving

NIKLAS SÖRENSSON

Department of Computer Science and Engineering Chalmers University of Technology and University of Gothenburg SE-412 96 Göteborg Sweden

Göteborg, September 2008

Effective SAT Solving NIKLAS SÖRENSSON ISBN 978-91-628-7612-8

$\odot$  Niklas Sörensson, 2008

Technical report no. 45D Department of Computer Science and Engineering Division of Software Engineering and Technology

Department of Computer Science and Engineering Chalmers University of Technology and University of Gothenburg SE-412 96 Göteborg Sweden Telephone + 46 (0)31–772 1000

Printed at Chalmers, Göteborg, Sweden, 2008

#### Abstract

A growing number of problem domains are successfully being tackled by SAT solvers. This thesis contributes to that trend by pushing the state-of-the-art of core SAT algorithms and their implementation, but also in several important application areas. It consists of five papers: the first details the implementation of the SAT solver MINISAT and the other four papers discuss specific issues related to different application domains.

In the first paper, catering to the trend of extending and adapting SAT solvers, we present a detailed description of MINISAT, a SAT solver designed for that particular purpose. The description additionally bridges a gap between theory and practice, serving as a tutorial on modern SAT solving algorithms. Among other things, we describe how to solve a series of related SAT problems efficiently, called incremental SAT solving.

For finding finite first order models the MACE-style method that is based on SAT solving is well-known. In the second paper we improve the basic method with several techniques that can be loosely classified as either transformations that make the reduction to SAT result in fewer clauses or techniques that are designed to speed up the search of the SAT solver. The resulting tool, called PARADOX, won the SAT/Models division of the CASC competition in 2003 and has not been beaten since by a single general purpose model finding tool.

In the last decade the interest in methods for safety property verification that are based on SAT solving has been steadily growing. One example of such a method is temporal induction. The method requires a sequence of increasingly stronger induction proofs to be performed. In the third paper we show how this sequence of proofs can be solved efficiently using incremental SAT solving.

The last two papers consider two frequently occurring types of encodings: (1) the problem of encoding circuits into CNF, and (2) encoding 0-1 integer linear programming into CNF and how to use incremental SAT to solve the intended optimization problem.

There are several encoding patterns that occur over and over again in this thesis but also elsewhere. The most noteworthy are: incremental SAT, lazy encoding of constraints, and bit-wise encoding of arithmetic influenced by hardware designs for adders and multipliers.

The general conclusion is: deploying SAT solvers effectively requires implementations that are efficient, yet easily adaptable to specific application needs. Moreover, to get the best results, it is worth spending effort to make sure that one uses the best codings possible for an application. However, it is important to note that this is not absolutely necessary. For some applications naive problem codings work just fine which is indeed part of the appeal of using SAT solving.

# Acknowledgments

I'd like to thank everybody that has in some way helped me during my PhD studies. In particular, I would like to thank some without whom this work would never have come to be:

My supervisors Koen Claessen and Reiner Hähnle, for being as responsible and supportive as you could wish supervisors to be, and for mastering the delicate art of applying just the right amount of pressure.

A bit outside the normal responsibilities of a supervisor, Reiner's influence has helped me learn to appreciate Wine.

Koen, for his friendship, enthusiasm<sup>1</sup>, and ability to discuss any topic, technical or not.

Mary Sheeran, for fostering the special atmosphere in the Formal Methods group, and stimulated a whole generation of PhD students to be interested in SAT solving.

Niklas Een, for being a great friend and the best co-worker I've had the pleasure to work with. I hope that we will have more chances to collaborate in the future. As a sign of my humble gratitude: I forgive you for forcing me to use (and appreciate) an indentation depth of 4 characters.

My family and friends, who has always encouraged me even when prospects were bleak. In particular, my beloved Cissi, whom have had to endure a lot during my efforts to write this thesis. Examples include, fits of frustration and/or despair, sleepless night, financial problems, missed vacations. The list goes on, but you have stayed with me. For that I'm forever grateful.

<sup>&</sup>lt;sup>1</sup> "Det låter jätteintressant! Men..."

# Contents

| 1 | $\mathbf{Intr}$ | oduction                                                | 3          |

|---|-----------------|---------------------------------------------------------|------------|

|   | 1.1             | SAT                                                     | 4          |

|   |                 | 1.1.1 The Origins of SAT Solving                        | 4          |

|   |                 | 1.1.2 The DPLL algorithmic framework                    | 5          |

|   |                 | 1.1.3 MiniSat                                           | 6          |

|   | 1.2             | Applications                                            | 7          |

|   | 1.3             | Contributions                                           | 9          |

|   | 1.4             |                                                         | 0          |

| 2 | An              | Extensible SAT-solver 1                                 | 2          |

|   | 2.1             | Introduction                                            | .3         |

|   | 2.2             | Application Programming Interface                       | .3         |

|   | 2.3             | Overview of the SAT-solver                              | .5         |

|   | 2.4             | Implementation                                          | 8          |

|   |                 | 2.4.1 The solver state                                  | 8          |

|   |                 | 2.4.2 Constraints                                       | 8          |

|   |                 | 2.4.3 Propagation                                       | 22         |

|   |                 | 2.4.4 Learning                                          | 22         |

|   |                 | 2.4.5 Search                                            | 26         |

|   |                 | 2.4.6 Activity heuristics                               | 28         |

|   |                 |                                                         | <b>3</b> 0 |

|   |                 |                                                         | <b>3</b> 0 |

|   | 2.5             | Conclusions and Related Work                            | 80         |

| 3 | New             | Techniques to Improve MACE-style Finite Model Finding 3 | 3          |

|   | 3.1             | Introduction                                            | 34         |

|   | 3.2             | Notation                                                | 35         |

|   | 3.3             | MACE-style Model Finding                                | 35         |

|   | 3.4             |                                                         | 37         |

|   | 3.5             | Incremental Search                                      | 39         |

|   | 3.6             | Static Symmetry Reduction                               | 11         |

|   | 3.7             | v v                                                     | 13         |

|   | 3.8             |                                                         | 15         |

|   | 3.9             |                                                         | 16         |

|   | 3.10            |                                                         | 17         |

| 4 |                   | aporal Induction by Incremental SAT Solving               | 49           |

|---|-------------------|-----------------------------------------------------------|--------------|

|   | 4.1               | Introduction                                              | 50           |

|   | 4.2               | Preliminaries                                             | 50           |

|   |                   | 4.2.1 The SAT problem                                     | 50           |

|   |                   | 4.2.2 Temporal Induction                                  | 51           |

|   | 4.3               | Incremental SAT                                           | 53           |

|   | 4.4               | Incremental Induction                                     | 54           |

|   |                   | 4.4.1 Discussion                                          | 55           |

|   |                   | 4.4.2 Improving the Unique States Requirement             | 57           |

|   | 4.5               | Experimental Results                                      | 59           |

|   | 4.6               | Related Work                                              | 63           |

|   | 4.7               | Conclusions                                               | 63           |

|   | 4.8               | Future Work                                               | 64           |

| 5 | Apı               | olying Logic Synthesis for Speeding Up SAT                | 65           |

|   | 5.1               | Introduction                                              | 66           |

|   | 5.2               | Preliminaries                                             | 66           |

|   | 5.3               | Cut Enumeration                                           | 67           |

|   | 5.4               | DAG-Aware Minimization                                    | 67           |

|   | 5.5               | CNF through the Tseitin Transformation                    | 69           |

|   | 5.6               | CNF through Technology Mapping                            | 70           |

|   |                   | 5.6.1 Definitions                                         | 70           |

|   |                   | 5.6.2 A Single Mapping Phase                              | 71           |

|   |                   | 5.6.3 The Cost of Cuts                                    | 71           |

|   |                   | 5.6.4 The Complete Mapping Procedure                      | 72           |

|   | 5.7               | Experimental Results                                      | 73           |

|   | 5.8               | Conclusions                                               | 74           |

|   | 5.9               | Acknowledgments                                           | 78           |

|   |                   |                                                           |              |

| 6 | <b>Tra</b><br>6.1 | nslating Pseudo-Boolean Constraints into SAT Introduction | <b>80</b> 81 |

|   | 6.2               | Preliminaries                                             | 82           |

|   | 6.3               | Normalization of PB-constraints                           | 82           |

|   | 6.4               | Optimization – the objective function                     | 84           |

|   | 6.5               | Translation of PB-constraints                             | 84           |

|   | 0.0               | 6.5.1 The Tseitin transformation                          | 85           |

|   |                   | 6.5.2 Pseudo-code Conventions                             |              |

|   |                   | 6.5.3 Translation through BDDs                            | 88           |

|   |                   | 6.5.4 Translation through Adder Networks                  |              |

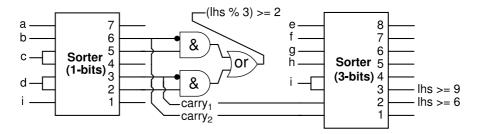

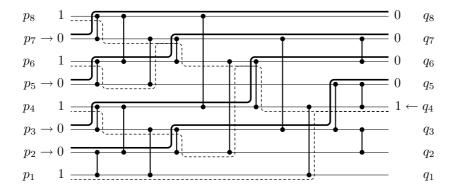

|   |                   | 6.5.5 Translation through Sorting Networks                | 90<br>93     |

|   | 6.6               | g g                                                       |              |

|   | 6.6               |                                                           | 100          |

|   |                   | r                                                         | 101          |

|   | 67                | , i                                                       | 103          |

|   | 6.7               |                                                           | 104          |

|   |                   |                                                           |              |

## Chapter 1

## Introduction

In formal logics there is a conflict between expressivness of logics on one end, and the ease with which the decision problems for said logics can be solved. The more expressive a logic is the harder it becomes to automatize. In the lower end of this scale there exist logics with decision procedure that run in polynomial time, but the expressiveness of such logics is usually very limited. At the other end of the scale, most higher-order logics are expressive enough to be the foundation for all of mathematics but they are then necessarily incomplete, in the sense that there are bound to be properties that appear to be true but are impossible to prove for any given (consistent) axiomatization. This remarkable fact is usually referred to as "Gödel's incompleteness theorem".

This thesis is mainly concerned with propositional logic, but it touches on issues in temporal logic and first order logic (FOL) as well. Propositional logic is in the lower end of the expressiveness scale: it allows you to state simple boolean properties constructed using *variables* and basic logical conjunctives such as *and*, *or*, *not*, and *implies*.

Propositional logic is expressive enough to be useful in practice, but there is no known algorithm for its decision problem that executes in polynomial time. In fact, it was the first problem proven to be NP-complete [Coo71] which essentially means that it can be seen as the canonical example of a problem that is "hard to solve". Nonetheless, considerable progress in practical terms was made in solving the satisfiability problem of propositional logic (called simply the "SAT problem" from now on) in the last decade. The SAT problem is at the core of this thesis and is discussed in Section 1.1 below.

Temporal logic increases expressivity compared to propositional logic in that it allows us to talk about time. For example, it is possible to model stateful system that evolve as time progresses. The price for this expressivity is that decision complexity is harder than for propositional logic, typically, PSPACE. The most popular technique for reasoning about temporal logic is called *Model Checking*.

First order logic goes beyond propositional logic in that one can model relations and functions over individual objects and, more importantly, it is possible to quantify over individuals. This capability pushes the first order decision problem into the realm of the undecidable, however, there exist various syntactic restrictions that render FOL decidable again.

It is important to note that first order logic is semi-decidable: given a first

order theorem, it is possible to prove it automatically in finite time. This is not possible for non-provable statements in general. This has the important consequence that finding counter examples for invalid first order statements is inherently hard. The crux of the matter is the (necessary) existence of statements that can only be refuted with infinitely large counter examples. A natural restriction is the limitation to finite counter examples, or even counter examples with a fixed bound.

It is well known from theoretical logic that logics can be encoded into each other and coding techniques have been used to prove a number of theoretical results. Only in the last years, however, coding techniques came into focus as a means to achieve practically useful algorithms. Thus, coding expressive features in a less expressive logic can been seen as (superficially) increasing the expressiveness of a logic, at the cost of lowering reasoning to potentially unnatural levels. A good example of this is finite arithmetic, which can be coded at the bit-level in propositional logic.

We say more on model checking, first order finite model finding, and encoding of logics in Section 1.2.

### 1.1 SAT

The satisfiability (SAT) problem is the problem of deciding whether the variables of a propositional formula can be assigned in such a way that the formula evaluates to true. The research area devoted to this problem is today very active as there have recently been an increased general interest in SAT. However, research into SAT algorithms has been going on for long time now. This section gives a short historical background on SAT research, followed by a description of our first contribution to the field, the SAT solver MINISAT.

#### 1.1.1 The Origins of SAT Solving

During the late 50's and early 60's a lot of the pioneering work on automated theorem proving was made possible by both the fact that general purpose computers were recently made readily available, and also, that computability had been anticipated in academia for a long time, and a lot of the theoretical ground-work had already been done. Among those experimenting with the first implementations of theorem provers were Martin Davis and Hilary Putnam, who wrote the paper describing what is believed to be the first program solving the SAT problem[DP60]. Although this paper really tackles first order theorem proving, it is best known and appreciated for the groundwork on SAT. The algorithm is based on quantifier elimination and removes the variables one-by-one from the problem, until either an empty clause is derived, which means the problem is unsatisfiable, or, all variables have been removed, meaning the problem is satisfiable.

The problem with this algorithm is that repeated quantifier elimination is very likely to grow the problem expontentially. Moreover, since computer memory was a particularily scarce resource at the time there was a necessity to trade memory for running time. This was part of the aim of the follow up work by Martin Davis, George Logemann and Donald W. Loveland[DLL62]. The algorithm they proposed for solving the SAT problem has some of the most crucial

aspects of modern SAT algorithms, such as branching/backtracking and unit propagation. This allows the algorithm to run in memory linear to the size of the problem, but may still take exponential time. For a more detailed elaboration, see the chapter *The early history of Automated Deduction* of [RV01].

#### 1.1.2 The DPLL algorithmic framework

The SAT algorithm usually referred to as DPLL should rather be seen as a framework of algorithms. The unique features that characterize DPLL are branching, backtracking, and unit propagation. These elements are tied together in a recursive procedure that systematically investigates the complete boolean state space in the following way: branching means that the problem is split into two subproblems, where a certain variable has been assigned true and false respectively. These subproblems can then be solved independently in any order. If there is some clause that is false given the current set of assignments, that part of the search space cannot contain any solutions. It is then necessary to backtrack, undoing all variable assignments, until the latest branch point that has not been tried with both values.

Branching and backtracking are in fact enough to form a complete procedure, in the sense that it will always find a solution, but it will be very inefficient. The problem is that, given a certain set of assignments to variables induced by a branch in the search, there may be a number of apparent consequential assignments to variables, and it would be very bad to try both values for them. Unit propagation is a procedure that derives such consequences for a very specific definition of "apparent": namely given that all literals but one of a clause has been given the value false, then one can conclude that the remaining literal must have the value true.

Branching Heuristics The most obvious degree of freedom is in which order to branch on variables. Over the years a large number of branching heuristics have been devised, but for a long time they were all quite similar in the sense that they used syntactic properties of the problem as guides. For example, by choosing the variable that satisfies the largest number of unresolved clauses (clauses that still contain unassigned literals), one might expect to quickly reduce the problem and possibly find a satisfying assignment faster. These kind of measures was usually weighted in some way with respect to how easily clauses could be satisfied, where satisfying a "hard" clause was worth more than an "easy" clause. A prominent example of this kind of heuristics is the Jeroslow-Wang heuristic [JW90], which worked relatively well at the time of it's inception. The motivation for why this heuristic worked well was later refuted by Hooker et al [HV95], which serves as a good example of the notorious difficulty in understanding and evaluating heuristics.

Another complication in the investigation of heuristics is the interdependence between different components of the algorithms. For instance, João Marques-Silva[Sil99] comes to the conclusion that the branching heuristic does not matter much in the precence of a modern learning implementation (outlined below), at least considering the heuristics available at the time.

This syntactic type of heuristics were dominant until the end of the nineties, when there was a major break-through with the arrival of the SAT solver CHAFF[MMZ<sup>+</sup>01b]. The branching heuristics introduced in CHAFF, named

Variable State Independent Decaying Sum (VSIDS), had two unique properties that made it very well adapted to the rest of the DPLL algorithm: (1) As the name implies it is not dependent on the current assignments to variables in a particular branch. This means that no extra work has to be done during unit propagation or backtracking, which makes these key procedures faster. In particular, it is no longer necessary to recognize exactly which clauses are unresolved, a fact that is crucial for allowing the particular implementation of unit propagation outlined below. (2) Instead of depending on syntactic properties of the problem, it is closely tied to the set of learned clauses. Informally, variables that occur often in recently learned clauses are preferred. The intention is that this will steer the search into a direction making the most out of the current set of learned clauses.

Another similar variable heuristic, the Berkmin heuristic [GN02], is based on the observation that the reason that the VSIDS heuristic works so well is that it tends to branch on variables occuring in recent clauses. The Berkmin heuristic achieves the same effect more directly by examining recently learnt clauses for candidate branching variables.

Efficient unit propagation Until recently, unit propagation used to be implemented with straight-forward techniques. However, the invention of clever data structures has changed this. *Head-tail lists* were introduced in SATO [ZS00] in order to reduce the amount of work in unit propagation. Most modern SAT solvers today use a method called *two literal watching*, pioneered in Chaff [MMZ<sup>+</sup>01b], which uses a similar datastructure to a somewhat better effect [LS05].

Learning With only the mechanisms outlined above it is very likely that a DPLL search procedure will run into conflicts that are essentially the same, in the sense that they depend on the same assignments, over and over again. To cope with this redundancy it is standard practice to deploy a learning procedure [SS96] that for each conflict derives a new learned clause, such that unit propagation alone will avoid the same conflict in the future. This learned clause is derived using *conflict analysis*, which essentially traces the reasons for assignments involved with the conflict. As a side effect the conflict analysis may reveal that there was in fact a number of assumptions not involved in the conflict, that can be skipped during backtracking. The branches for the other polarity of these assumptions can be skipped entirely, and this process is usually referred to as non-chronological backtracking.

#### 1.1.3 MiniSat

MINISAT and the accompanying paper that describes its implementation (Chapter 2) was first introduced as a write-up for SATZOO, one of the winning entries of the 2002 SAT competition. However, it was actually re-written from scratch (drawing from both SATZOO and SATNIK), and significantly simplified in the process. The aim was to produce a SAT solver that had state-of-the-art performance, and yet was small enough that essentially all the code could be included in full detail in the paper. The authors felt at the time that there was a need to provide more details on what was required to implement a modern SAT solver

— details that newcomers had to either figure out themselves or extract from reading the source-code of freely available solvers such as CHAFF and LIMMAT. Another goal was to make the implementation of MiniSat as easy as possible to pick up by others, and start hacking on it too. This was partly achieved by the simple design, but it was also important to distribute the source-code under an unrestrictive license.

Even though the implementation was minimalistic, we managed to sneak in some features outside of the core algorithms. Firstly, we provided a simple API to extend the solver with new types of boolean constraints, similar to the standard practice in the field of constraint programming. Secondly, we introduced another API for *incremental* SAT solving that was simpler than what had existed before, but still powerful enough to encode both addition and removal of clauses using a bit of extra coding.

While the first version of MINISAT was not quite as efficient as the solvers it was derived from, it was never very far behind. Moreover, it proved to be a very sound foundation to build further work on, as it has since caught-up with and significantly outperformed its predecessors.

For an overview of the significant impact of MINISAT, see Section 1.3.

### 1.2 Applications

Apart from the design and implementation of core SAT algorithms, this thesis also consists of several investigations into different application areas where SAT-solving plays a central role. Each of the four chapters after Chapter 2 is concerned with one such application area.

First Order Finite Model Finding As the dual to automated theorem proving for first order logic, model finding is a very important tool. In general, there are no complete automated methods for this, but finding models with finite domains is possible to do automatically. Chapter 3 is based on the paper New Techniques that Improve MACE-style Finite Model Finding, written together with Koen Claessen in 2003. The paper introduces significant improvements over the conventional way of finding finite models using a SAT solver, which we called MACE-style model finding, after McCune's model finding tool MACE2 [McC94]. We implemented our method in the tool PARADOX, which has consistently won the CASC competition in its division every year since 2003. Alternative methods for finite model finding are based on a direct search, and are implemented in tools such as SEM [JZ96] and MACE4 [McC03]. These methods can outperform SAT-based methods in some problem areas, but on the whole SAT-based model finding is very competitive.

**SAT-based Model Checking** For circuits with sequential behaviour *model checking* proved to be a highly successful verification technique. It is probably the single most successful formal verification procedure, as is demonstrated by the fact that some of the pioneers<sup>1</sup> in the area of Model Checking were recently given the Turing-award. Chapter 4 is based on the paper *Temporal Induction by Incremental SAT Solving*, written together with Niklas Eén in 2003. This

$<sup>^{1}\</sup>mathrm{Edmund}$  M. Clarke, E. Allen Emerson and Joseph Sifakis

paper describes in detail how an *induction based* model checking algorithm can be implemented using incremental SAT solving. The main challenge with this type of algorithm is that for each property the circuit may have to be unrolled an unknown number of times to a certain *depth*, in order to make the induction hypothesis strong enough. Before our paper it was standard practice to make an arbitrary guess and, if the depth was too small to prove the property, one would guess a larger depth and repeat the process. In the paper, we show that it is feasible to try *all* depths one after another using an incremental procedure. This achieves a greater level of automation as the user does not have to make any guesses.

Circuit to CNF encoding SAT solvers usually accept input formulas in Conjunctive Normal Form (CNF). However, it is commonly the case that problem domains require reasoning about circuits, or simply need the flexibility given by general propositional formulas. In these cases it is possible to translate a circuit or a propositional formula to an equivalent formula in CNF, but these translations are not very useful as they will increase the formula size exponentially in general. This problem is possible to get around with translations that are allowed to introduce new fresh variables for internal points in the circuit or formula. The most well-known and often-used such translation is the Tseitin [Tse68] transformation which is very simple yet useful in practice. Chapter 5 is based on the paper Applying Logic Synthesis for Speeding Up SAT, co-authored by Niklas Eén and Alan Mishchenko in 2007. In this paper we explore two techniques for Circuit to CNF encoding that are more elaborate than the Tseitin transformation with the intention to produce encodings that are smaller. The first technique, DAG-Aware minimization, is used as a pre-processing step and is designed to reduce redundancy in the circuit itself. This technique is not new, but its effect on runtimes of SAT solving is isolated and presented in more detail than what has been done before. The second technique, the actual CNF encoding, is novel, and it puts standard FPGA technology mapping algorithms to the use of minimizing the number of clauses in the result. The appeal of this approach is that the heuristics used are of a more global flavour compared to other commonly used improvements to the Tseitin transformation.

**0-1 Integer Linear Programming** The optimization of a linear function, subject to a set of linear constraints, is referred to as *linear programming*. An important special case is when the variables of the objective function and constraints are restricted to be either zero or one. The resulting type of problem is known as *0-1 integer linear programming* (ILP) and it has a certain propositional flavour to it. Therefore, it is natural to investigate the relation between 0-1 ILP and the SAT problem. Chapter refcha:minisatplus is based on the paper *Translating Pseudo-Boolean Constraints into SAT* co-authored by Niklas Eén in 2005. In this paper we investigate several ways of translating 0-1 linear constraints into CNF. We were at first interested in how a translation based approach could compare to methods that were based on extensions of SAT algorithms and produced a solver called MINISAT+. As the results seemed promising, we were intrigued enough to try to better understand the relative merits of the different encodings we used. One important conclusion was that while the size of the CNF clearly matters, a smaller encoding is not always

better. In such cases, the notion of arc-consistency helps explain why a more verbose encoding may be preferable. Essentially, an encoding that preserves arc-consistency makes unit propagation more powerful which in turn avoids useless repetition for the SAT solver. We then prove that the novel translation technique based on sorter networks is arc-concistent for the special case of linear constraints known as cardinality constraints.

### 1.3 Contributions

The release of the source-code of MINISAT and the paper documenting the implementation [ES03a] have been well received in the SAT community. There are three reasons for this: (1) MINISAT it is easy to understand, (2) it is easy to adapt or extend with new features, and (3) its efficiency has remained state-of-the-art within the academic setting. The following provide some evidence of these points:

Winning SAT Competitions MINISAT first won the industrial track of the SAT competition in 2005 together with the CNF preprocessor SATELITE. In 2006 MINISAT 2.0 won the light-weight SAT competition in the SAT-Race organized in between the bi-annual SAT competition. The main new feature was a reimplementation of the preprocessor from SATELITE but the efficiency of the resulting solver was mostly the same as the previous year. The coming year MINISAT had not been updated at all and in the next SAT competition the rest of the world had caught up and improved upon MINISAT. The now rather old implementation still got second and third place in three of the industrial tracks of the year 2007 competition. In 2008, MINISAT 2.1 again won the main track of the SAT-Race.

Usages or extensions MINISAT is used in a large number of applications and tools within automated theorem proving as well as software- and hardware verification. One of the earliest adopters is the Satisfiability Modulo Theories (SMT) solver MATHSAT [BBC+05]. Another similar system that extends MINISAT is OPENSMT [BS], which also shares the MINISAT-philosophy of providing a simple, open, and easy-to-extend architechture for the benefit of the research community. In first-order theorem proving, instantiation-based methods currently have a renaissance and they are built upon SAT solvers. The at present strongest instantiation-based system IPROVER [Kor08] is using MINISAT.

Language ports The small code-base of MINISAT has made it feasible to make feature-complete translations to programming languages other than C++. For instance, SAT4J [Ber] is a comprehensive modular Java library for SAT solving and other related combinatorial problems. The part providing a configurable SAT solver contains a translation of many MINISAT algorithms (some parts could apparently almost be copied as-is). Another example is the C-version of MINISAT; while originally written by the MINISAT authors, this has been picked up and improved in the system ABC [SG] by Alan Mishchenko. Another, apparently rather straightforward, port to C# also exists [Mos07].

From a few years of experience with MINISAT, it can be concluded that a SAT solver does not have to be complicated to be efficient. In some sense, this can be interpreted as the superiority of brute force approaches over cleverness. So in effect, the simplicity of the algorithms comes at the price that it is very hard to improve upon the current state-of-the-art. This can be seen by the fact that progress on core algorithms and implementations is rather slow, even with the increased interest the SAT community has enjoyed in the past few years. Put simply, there are not a lot of low hanging fruit in the domain of core algorithms for SAT solving.

Besides the open architecture of a SAT solver, an additional category of contributions of this thesis lies in the development of encoding techniques for a number of different applications (Chapters 3–6). Taken as a whole, this has helped to emphasize the importance of encodings within the SAT community. There are several encoding patterns that occur over and over again. The most noteworthy are: incremental SAT, lazy encoding of constraints, and bit-wise encoding of arithmetic influenced by hardware designs for adders and multipliers. These have shown themselves to be extremely useful tools in the effective use of a SAT-solver for tackling problems in different areas, and should be part of the arsenal of anyone attacking a new problem area.

#### 1.4 Discussion

We close this chapter with some critical considerations on the state of affairs with regard to the Scientific Method in the subcommunity of Computer Science where our work takes place. This should in no way be understood as criticsm of any individual researchers or research group, but as a (self-)critical reflection on how scientific progress can be ensured better than it is currently done.

The issue we would like to discuss is the transitional difficulties that the formal verification community is suffering from, by having gone from a purely theoretical field (as a part of mathematical logic) to a more mixed discipline with strong flavours of engineering and experimental science. It seems that the attitude of the community has not fully adapted to accommodate the additional principles that have to be followed. A publication in theoretical computer science can be verified simply by reading and understanding the material, but results based on experiments require that the experiments can be repeated by others.

**Repeatability** Experimental results may be hard to repeat for different reasons: (1) The conclusions only apply to a very narrow set of problems. (2) They are dependent on factors not mentioned in the paper. This in turn may be either for space restriction (i.e. page-limit) reasons, or simply because the authors did not know that the dependency exists. (3) Errors were introduced in the (original) evaluation procedure itself.

It is important, that given a failure to repeat a certain result, one should be able to determine whether the error is on ones own behalf or one of the cases above holds. In the field of formal verification, for this to be possible, both benchmarks and implementations used in the experiments need to be published; otherwise, you cannot rule out both (1) and (2). This usually poses a problem to researchers who work in (or in collaboration with) industry. Benchmarks

that are derived from customers, or otherwise contain sensitive data, are simply impossible to share with the public. The implementations used in experiments are often part of some product, and cannot be shared in order to maintain trade secrets.

What could be done? Note that it is by no means only experimental industrial research that lacks the accompanying benchmarks or source code. It seems the community would do well to foster an attitude change so that researchers working in a non-commercial context always provide all the necessary means to reproduce the experiments of a publication. It is, of course, important to accomodate the justified interests of industrial research. Clearly, academic research benefits from tight communication with industry and severing that connection is counter-productive.

One possibility to improve the situation is to reinforce the importance of gathering and maintaining a public body of benchmarks for different problem categories. There already exist such efforts for different subcommunities<sup>2</sup>, but there is room for improvement as such collections rarely are comprehensive.

Another trend that is improving on this situation is the growing number of high quality, open, implementations of various theorem proving software of which MINISAT is but one example. This is makes it possible, at least in principle, to implement new ideas on a basis that is independent of trade secrets. Such practice allows disclosure of implementations in more cases.

$<sup>^2\</sup>mathrm{A}$  good example is Thousands Of Problems For Theorem Proving (TPTP) [SS07].

## Chapter 2

## An Extensible SAT-solver

Niklas Eén, Niklas Sörensson Chalmers University of Technology and Göteborg University

#### Abstract

In this article, we present a small, complete, and efficient SAT-solver in the style of conflict-driven learning, as exemplified by CHAFF. We aim to give sufficient details about implementation to enable the reader to construct his or her own solver in a very short time. This will allow users of SAT-solvers to make domain specific extensions or adaptions of current state-of-the-art SAT-techniques, to meet the needs of a particular application area. The presented solver is designed with this in mind, and includes among other things a mechanism for adding arbitrary boolean constraints. It also supports solving a series of related SAT-problems efficiently by an incremental SAT-interface.

### 2.1 Introduction

The use of SAT-solvers in various applications is on the march. As insight on how to efficiently encode problems into SAT is increasing, a growing number of problem domains are successfully being tackled by SAT-solvers. This is particularly true for the *electronic design automation* (EDA) industry [BCC<sup>+</sup>99, Lar92]. The success is further magnified by current state-of-the-art solvers being extended and adapted to meet the specific characteristics of these problem domains [ARMS02a, ES03b].

However, modifying an existing solver, even with a thorough understanding of both the problem domain and of modern SAT-techniques, can become a time consuming and bewildering journey into the mysterious inner workings of a tenthousand-line software package. Likewise, writing a solver from scratch can also be a daunting task, as there are numerous pitfalls hidden in the intricate details of a correct and efficient solver. The problem is that although the *techniques* used in a modern SAT-solver are well documented, the details necessary for an *implementation* have not been adequately presented before.

In the fall of 2002, the authors implemented the solvers SATZOO and SATNIK. In order to sufficiently understand the implementation tricks needed for a modern SAT-solver, it was necessary to consult the source-code of previous implementations. <sup>1</sup> We find that the material contained therein can be made more accessible, which is desirable for the SAT-community. Thus, the principal goal of this article is to bridge the gap between existing descriptions of SAT-techniques and their actual implementation.

We will do this by presenting the code of a minimal SAT-solver MINISAT, based on the ideas for conflict-driven backtracking [SS96], together with watched literals and dynamic variable ordering [MMZ+01b]. The original C++ source code (downloadable from http://www.cs.chalmers.se/~een) for MINISAT is under 600 lines (not counting comments), and is the result of rethinking and simplifying the designs of SATZOO and SATNIK without sacrificing efficiency. We will present all the relevant parts of the code in a manner that should be accessible to anyone acquainted with either C++ or Java.

The presented code includes an incremental SAT-interface, which allows for a series of related problems to be solved with potentially huge efficiency gains [ES03b]. We also generalize the expressiveness of the SAT-problem formulation by providing a mechanism for arbitrary *constraints* over boolean variables to be defined. Paragraphs discussing implementation alternatives are marked "[Disc]" and can be skipped on a first reading.

From the documentation in this paper we hope it is possible for *you* to implement a fresh SAT-solver in your favorite language, or to grab the C++ version of MINISAT from the net and start modifying it to include new and interesting ideas.

### 2.2 Application Programming Interface

We start by presenting MINISAT's external interface, with which a user application can specify and solve SAT-problems. A basic knowledge about SAT is

$<sup>^1</sup>LIMMAT$  at http://www.inf.ethz.ch/personal/biere/projects/limmat/, ZCHAFF at http://www.ee.princeton.edu/~chaff/zchaff

assumed (see for instance [SS96]). The types *var*, *lit*, and *Vec* for variables, literals, and vectors respectively are explained in detail in section 2.4.

```

class Solver - Public interface

new Var

var

bool

addClause

(Vec\langle lit\rangle literals)

bool

add...

(\ldots)

bool

simplifyDB ()

bool

solve

(Vec\langle lit\rangle \text{ assumptions})

- If found, this vector has the model.

Vec\langle bool \rangle model

```

The "add..." method should be understood as a place-holder for additional constraints implemented in an extension of MINISAT.

For a standard SAT-problem, the interface is used in the following way: Variables are introduced by calling newVar(). From these variables, clauses are built and added by addClause(). Trivial conflicts, such as two unit clauses  $\{x\}$  and  $\{\overline{x}\}$  being added, can be detected by addClause(), in which case it returns FALSE. From this point on, the solver state is undefined and must not be used further. If no such trivial conflict is detected during the clause insertion phase, solve() is called with an empty list of assumptions. It returns FALSE if the problem is unsatisfiable, and TRUE if it is satisfiable, in which case the model can be read from the public vector "model".

The simplifyDB() method can be used before calling solve() to simplify the set of problem constraints (often called the  $constraint\ database$ ). In our implementation, simplifyDB() will first propagate all unit information, then remove all satisfied constraints. As for addClause(), the simplifier can sometimes detect a conflict, in which case FALSE is returned and the solver state is, again, undefined and must not be used further.

If the solver returns satisfiable, new constraints can be added repeatedly to the existing database and solve() run again. However, more interesting sequences of SAT-problems can be solved by the use of unit assumptions. When passing a non-empty list of assumptions to solve(), the solver temporarily assumes the literals to be true. After finding a model or a contradiction, these assumptions are undone, and the solver is returned to a usable state, even when solve() return FALSE, which now should be interpreted as unsatisfiable under assumptions.

For this to work, calling simplifyDB() before solve() is no longer optional. It is the mechanism for detecting conflicts independent of the assumptions – referred to as a top-level conflict from now on – which puts the solver in an undefined state. We wish to remark that the ability to pass unit assumptions to solve() is more powerful than it might appear at first. For an example of its use, see [ES03b].

An alternative interface would be for solve() to return one of three values: satisfiable, unsatisfiable, or unsatisfiable under assumptions. This is indeed a less error-prone interface as there is no longer a pre-condition on the use of solve(). The current interface, however, represents the smallest modification of a non-incremental SAT-solver. The early non-incremental version of SATZOO was made compliant to the above interface by adding just 5 lines of code.

#### 2.3 Overview of the SAT-solver

This article will treat the popular style of SAT-solvers based on the DPLL algorithm [DLL62], backtracking by conflict analysis and clause recording (also referred to as *learning*) [SS96], and boolean constraint propagation (BCP) using watched literals [MMZ<sup>+</sup>01b].<sup>2</sup> We will refer to this style of solver as a conflict-driven SAT-solver.

The components of such a solver, and indeed a more general constraint solver, can be conceptually divided into three categories:

- Representation. Somehow the SAT-instance must be represented by internal data structures, as must any derived information.

- Inference. Brute force search is seldom good enough on its own. A solver also needs some mechanism for computing and propagating the direct implications of the current state of information.

- Search. Inference is almost always combined with search to make the solver complete. The search can be viewed as another way of deriving information.

A standard conflict-driven SAT-solver can represent *clauses* (with two literals or more) and *assignments*. Although the assignments can be viewed as unit-clauses, they are treated specially in many ways, and are best viewed as a separate type of information.

The only inference mechanism used by a standard solver is *unit propagation*. As soon as a clause becomes *unit* under the current assignment (all literals except one are false), the remaining unbound literal is set to true, possibly making more clauses unit. The process is continued until no more information can be propagated.

The search procedure of a modern solver is the most complex part. Heuristically, variables are picked and assigned values (assumptions are made), until the propagation detects a conflict (all literals of a clause have become false). At that point, a so called conflict clause is constructed and added to the SAT problem. Assumptions are then canceled by backtracking until the conflict clause becomes unit, from which point this unit clause is propagated and the search process continues.

MINISAT is extensible with arbitrary boolean constraints. This will affect the representation, which must be able to store these constraints; the inference, which must be able to derive unit information from these constraints; and the search, which must be able to analyze and generate conflict clauses from the constraints. The mechanism we suggest for managing general constraints is very lightweight, and by making the dependencies between the SAT-algorithm and the constraints implementation explicit, we feel it rather adds to the clarity of the solver than obscures it.

**Propagation.** The propagation procedure of MINISAT is largely inspired by that of CHAFF [MMZ<sup>+</sup>01b]. For each literal, a list of constraints is kept. These are the constraints that may propagate unit information (variable assignments)

<sup>&</sup>lt;sup>2</sup>This includes SAT-solvers such as: ZCHAFF, LIMMAT, BERKMIN.

if the literal becomes True. For clauses, no unit information can be propagated until all literals except one have become False. Two unbound literals p and q of the clause are therefore selected, and references to the clause are added to the lists of  $\overline{p}$  and  $\overline{q}$  respectively. The literals are said to be watched and the lists of constraints are referred to as  $watcher \ lists$ . As soon as a watched literal becomes True, the constraint is invoked to see if information may be propagated, or to select new unbound literals to be watched.

A feature of the watcher system for clauses is that on backtracking, no adjustment to the watcher lists need to be done. Backtracking is therefore very cheap. However, for other constraint types, this is not necessarily a good approach. MINISAT therefore supports the optional use of *undo lists* for those constraints; storing what constraints need to be updated when a variable becomes unbound by backtracking.

Learning. The learning procedure of MINISAT follows the ideas of Marques-Silva and Sakallah in [SS96]. The process starts when a constraint becomes conflicting (impossible to satisfy) under the current assignment. The conflicting constraint is then asked for a set of variable assignments that make it contradictory. For a clause, this would be all the literals of the clause (which are FALSE under a conflict). Each of the variable assignments returned must be either an assumption of the search procedure, or the result of some propagation of a constraint. The propagating constraints are in turn asked for the set of variable assignments that forced the propagation to occur, continuing the analysis backwards. The procedure is repeated until some termination condition is fulfilled, resulting in a set of variable assignments that implies the conflict. A clause prohibiting that particular assignment is added to the clause database. This learnt clause must always, by construction, be implied by the original problem constraints.

Learnt clauses serve two purposes: they drive the backtracking (as we shall see) and they speed up future conflicts by "caching" the reason for the conflict. Each clause will prevent only a constant number of inferences, but as the recorded clauses start to build on each other and participate in the unit propagation, the accumulated effect of learning can be massive. However, as the set of learnt clauses increase, propagation is slowed down. Therefore, the number of learnt clauses is periodically reduced, keeping only the clauses that seem useful by some heuristic.

**Search.** The search procedure of a conflict-driven SAT-solver is somewhat implicit. Although a recursive definition of the procedure might be more elegant, it is typically described (and implemented) iteratively. The procedure will start by selecting an unassigned variable x (called the *decision variable*) and assume a value for it, say True. The consequences of x=True will then be propagated, possibly resulting in more variable assignments. All variables assigned as a consequence of x is said to be from the same *decision level*, counting from 1 for the first assumption made and so forth. Assignments made before the first assumption (decision level 0) are called top-level.

All assignments will be stored on a stack in the order they were made; from now on referred to as the *trail*. The trail is divided into decision levels and is used to undo information during backtracking.

The decision phase will continue until either all variables have been assigned, in which case we have a model, or a conflict has occurred. On conflicts, the learning procedure will be invoked and a conflict clause produced. The trail will be used to undo decisions, one level at a time, until precisely one of the literals of the learnt clause becomes unbound (they are all FALSE at the point of conflict). By construction, the conflict clause cannot go directly from conflicting to a clause with two or more unbound literals. If the clause remains unit for several decision levels, it is advantageous to chose the lowest level (referred to as backjumping or non-chronological backtracking [SS96]).

```

loop

propagate()

- propagate unit clauses

if not conflict then

if all variables assigned then

return Satisfiable

else

decide()

- pick a new variable and assign it

else

- analyze conflict and add a conflict clause

if top-level conflict found then

return Unsatisfiable

else

backtrack()

- undo assignments until conflict clause is unit

```

An important part of the procedure is the heuristic for decide(). Like CHAFF, MINISAT uses a dynamic variable order that gives priority to variables involved in recent conflicts.

Although this is a good default order, domain specific heuristics have successfully been used in various areas to improve the performance [Str00]. Variable ordering is a traditional target for improving SAT-solvers.

**Activity heuristics.** One important technique first introduced with CHAFF [MMZ<sup>+</sup>01b] is a dynamic variable ordering based on activity (referred to as the VSIDS heuristic). The original heuristic imposes an order on *literals*, but borrowing from SATZOO, we make no distinction between p and  $\overline{p}$  in MINISAT.

Each variable has an *activity* attached to it. Every time a variable occurs in a recorded conflict clause, its activity is increased. We will refer to this as *bumping*. After recording the conflict, the activity of all the variables in the system are multiplied by a constant less than 1, thus *decaying* the activity of variables over time. Recent increments count more than old. The current sum determines the activity of a variable.

In MINISAT we use a similar idea for clauses. When a learnt clause is used in the analysis process of a conflict, its activity is bumped. Inactive clauses are periodically removed.

Constraint removal. The constraint database is divided into two parts: the problem constraints and the learnt clauses. As we have noted, the set of learnt clauses can be periodically reduced to increase the performance of propagation. Learnt clauses are used to crop future branches in the search tree, so we risk

getting a bigger search space instead. The balance between the two forces is delicate, and there are SAT-instances for which a big learnt clause set is advantageous, and others where a small set is better. MINISAT's default heuristic starts with a small set and gradually increases the size.

Problem constraints can also be removed if they are satisfied at the top-level. The API method simplifyDB() is responsible for this. The procedure is particularly important for incremental SAT-problems, where techniques for clause removal build on this feature.

**Top-level solver.** Although the pseudo-code for the search procedure presented above suffices for a simple conflict-driven SAT-solver, a solver *strategy* can improve the performance. A typical strategy applied by modern conflict-driven SAT-solvers is the use of *restarts* to escape from futile parts of the search tree. In MINISAT we also vary the number of learnt clauses kept at a given time. Furthermore, the *solve()* method of the API supports incremental assumptions, not handled by the above pseudo-code.

### 2.4 Implementation

The following conventions are used in the code. Atomic types start with a lower-case letter and are passed by value. Composite types start with a capital letter and are passed by reference. Blocks are marked only by indentation level. The bottom symbol  $\bot$  will always mean undefined; the symbol FALSE will be used to denote the boolean false.

We will use, but not specify an implementation of, the following abstract data types:  $Vec\langle T \rangle$  an extensible vector of type T; lit the type of literals containing a special literal  $\perp_{lit}$ ; lbool for the lifted boolean domain containing elements  $True_{\perp}$ ,  $False_{\perp}$ , and  $\perp$ ;  $Queue\langle T \rangle$  a queue of type T. We also use var as a type synonym for int (for implicit documentation) with the special constant  $\perp_{var}$ . The interfaces of the abstract data types are presented in Figure 2.1.

#### 2.4.1 The solver state

A number of things need to be stored in the solver state. Figure 2.2 shows the complete set of member variables of the solver type of MINISAT. Together with the state variables we define some short helper methods in Figure 2.3, as well as the interface of VarOrder (Figure 2.4), explained in section 2.4.6.

The state does *not* contain a boolean "conflict" to remember if a top-level conflict has been reached. Instead we impose as an invariant that the solver must never be in a conflicting state. As a consequence, any method that puts the solver in a conflicting state must communicate this. Using the solver object after this point is illegal. The invariant makes the interface slightly more cumbersome to use, but simplifies the implementation, which is important when extending and experimenting with new techniques.

#### 2.4.2 Constraints

MINISAT can handle arbitrary constraints over boolean variables through the abstraction presented in Figure 2.5. Each constraint type needs to implement

```

class lit - Public interface

class Vec\langle T \rangle – Public interface

lit (var x)

- Constructors:

Vec()

Global functions:

Vec(int \text{ size})

op \neg (lit p)

Vec(int \text{ size}, T \text{ pad})

bool sign (lit p)

- Size operations:

int var (lit p)

int index (lit p)

int size

void shrink

(int nof_elems)

class lbool – Public interface

void pop

lbool () lbool (bool x)

void growTo (int size)

void growTo (int size, T pad)

Global functions:

{m void} {\it clear}

lbool op \neg (lbool x)

- Stack interface:

- Global constants:

void push

lbool False, True, \perp

void push

(T \text{ elem})

last

class Queue\langle T \rangle - Public interface

Vector interface:

Queue ()

op [] (int index)

void insert

(T x)

- Duplicatation:

dequeue ()

void \ copyTo \ (Vec \langle T \rangle \ copy)

void clear

()

void moveTo (Vec \langle T \rangle dest)

int size

()

```

Figure 2.1: Basic abstract data types used throughout the code. The vector data type can push a default constructed element by the push() method with no argument. The moveTo() method will move the contents of a vector to another vector in constant time, clearing the source vector. The literal data type has an index() method which converts the literal to a "small" integer suitable for array indexing. The var() method returns the underlying variable of the literal, and the siqn() method if the literal is signed (FALSE for x and TRUE for  $\overline{x}$ ).

methods for constructing, removing, propagating and calculating reasons. In addition, methods for simplifying the constraint and updating the constraint on backtrack can be specified. We explain the meaning and responsibilities of these methods in detail:

Constructor. The constructor may only be called at the top-level. It must create and add the constraint to appropriate watcher lists after enqueuing any unit information derivable under the current top-level assignment. Should a conflict arise, this must be communicated to the caller.

**Remove.** The remove method supplants the destructor by receiving the solver state as a parameter. It should dispose the constraint and remove it from the watcher lists.

**Propagate.** The propagate method is called if the constraint is found in a watcher list during propagation of unit information p. The constraint is removed from the list and is required to insert itself into a new or the same watcher list. Any unit information derivable as a consequence of p should be enqueued. If successful, True is returned; if a conflict is

```

class Solver

Constraint database

Vec \langle Constr \rangle constrs

- List of problem constraints.

Vec\langle Clause\rangle learnts

- List of learnt clauses.

double

- Clause activity increment - amount to bump with.

cla_inc

double

cla_decay - Decay factor for clause activity.

Variable order

Vec⟨double⟩ activity

- Heuristic measurement of the activity of a variable.

double

- Variable activity increment - amount to bump with.

var_inc

double

var_decay - Decay factor for variable activity.

VarOrder

- Keeps track of the dynamic variable order.

Propagation

Vec \langle Vec \langle Constr \rangle \rangle

- For each literal 'p', a list of constraints watching 'p'.

A constraint will be inspected when 'p' becomes true.

watches

Vec \langle Vec \langle Constr \rangle \rangle

- For each variable 'x', a list of constraints that need to

undos

update when 'x' becomes unbound by backtracking.

propQ

Queue\langle lit \rangle

- Propagation queue.

- Assignments

Vec\langle lbool \rangle

assigns

- The current assignments indexed on variables.

Vec\langle lit \rangle

trail

- List of assignments in chronological order.

Vec\langle int \rangle

trail\_lim

- Separator indices for different decision levels in 'trail'.

- For each variable, the constraint that implied its value.

Vec \langle Constr \rangle

reason

Vec\langle int \rangle

level

- For each variable, the decision level it was assigned.

int

root_level - Separates incremental and search assumptions.

```

Figure 2.2: Internal state of the solver.

```

Solver.nVars()

int

return assigns.size()

int

Solver.nAssigns()

return trail.size()

Solver.nConstraints()

return constrs.size()

int

int

Solver.nLearnts()

return learnts. size()

return assigns[x]

lbool Solver.value(var x)

lbool Solver.value(lit p)

return sign(p) ? \neg assigns[var(p)] : assigns[var(p)]

Solver.decisionLevel()

return trail_lim.size()

```

Figure 2.3: Small helper methods. For instance, nLearnts() returns the number of learnt clauses.

```

class VarOrder − Public interface

VarOrder (Vec⟨lbool⟩ ref_to_assigns, Vec⟨double⟩ ref_to_activity)

void newVar() − Called when a new variable is created.

void update(var x) − Called when variable has increased in activity.

void updateAll() − Called when all variables have been assigned new activities.

void undo(var x) − Called when variable is unbound (may be selected again).

var select() − Called to select a new, unassigned variable.

```

Figure 2.4: Assisting ADT for the dynamic variable ordering of the solver. The constructor takes references to the assignment vector and the activity vector of the solver. The method select() will return the unassigned variable with the highest activity.

Figure 2.5: Abstract base class for constraints.

detected, FALSE is returned. The constraint may add itself to the undo list of var(p) if it needs to be updated when p becomes unbound.

**Simplify.** At the top-level, a constraint may be given the opportunity to simplify its representation (returns TRUE) or state that the constraint is satisfied under the current assignment (returns FALSE). A constraint must *not* be simplifiable to produce unit information or to be conflicting; in that case the propagation has not been correctly defined.

**Undo.** During backtracking, this method is called if the constraint added itself to the undo list of var(p) in propagate(). The current variable assignments are guaranteed to be identical to that of the moment before propagate() was called.

Calculate Reason. This method is given a literal p and an empty vector. The constraint is the reason for p being true, that is, during propagation, the current constraint enqueued p. The received vector is extended to include a set of assignments (represented as literals) implying p. The current variable assignments are guaranteed to be identical to that of the moment before the constraint propagated p. The literal p is also allowed to be the special constant  $\perp_{lit}$  in which case the reason for the clause being conflicting should be returned through the vector.

The code for the *Clause* constraint is presented in *Figure 2.7*. It is also used for learnt clauses, which are unique in that they can be added to the clause database while the solver is not at top-level. This makes the constructor code a bit more complicated than it would be for a normal constraint.

Implementing the addClause() method of the solver API is just a matter of calling Clause\_new() and pushing the new constraint on the "constrs" vector, storing the list of problem constraints. For completeness, we also display the code for creating variables in the solver (Figure 2.6).

```

var\ Solver.newVar()

int\ index

index = nVars()

watches\ .push()

watches\ .push()

undos\ .push()

reason\ .push(Null)

assigns\ .push(\bot)

level\ .push(-1)

activity\ .push(0)

order\ .newVar()

return\ index

```

Figure 2.6: Creates a new SAT variable in the solver.

There are a number of tricks for smart-coding that can be used in a C++ implementation of *Clause*. In particularly the "lits" vector can be implemented as an zero-sized array placed last in the class, and then extra memory allocated for the clause to contain the data. We observed a

20% speedup for this trick. Furthermore, memory can be saved by not storing activity for problem clauses.

Of the methods defining a constraint, propagate() should be the primary target for efficient implementation. The SAT-solver spends about 80% of the time propagating, so the method will be called frequently. In SATZOO a performance gain was achieved by remembering the position of the last watched literal and start looking for a new literal to watch from that position. Further speedups may be achieved by specializing the code for small clause sizes.

#### 2.4.3 Propagation

Given the mechanism for adding constraints, we now move on to describe the propagation of unit information on these constraints.

The propagation routine keeps a set of literals (unit information) that is to be propagated. We call this the *propagation queue*. When a literal is inserted into the queue, the corresponding variable is immediately assigned. For each literal in the queue, the watcher list of that literal determines the constraints that may be affected by the assignment. Through the interface described in the previous section, each constraint is asked by a call to its *propagate()* method if more unit information can be inferred, which will then be enqueued. The process continues until either the queue is empty or a conflict is found.

An implementation of this procedure is displayed in *Figure 2.9*. It starts by dequeuing a literal and clearing the watcher list for that literal by moving it to "tmp". The propagate method is then called for each constraint of "tmp". This will re-insert watches into new lists. Should a conflict be detected during the traversal of "tmp", the remaining watches will be copied back to the original watcher list, and the propagation queue cleared.

The method for enqueuing unit information is relatively straightforward. Note that the same fact can be enqueued several times, as it may be propagated from different constraints, but it will only be put on the propagation queue once.

It may be that later enqueuings have a "better" reason (determined heuristically) and a small performance gain was achieved in SATZOO by changing reason if the new reason was smaller than the previously stored. The changing affects the conflict clause generation described in the next section.

#### 2.4.4 Learning

This section describes the conflict-driven clause learning. It was first described in [SS96] and is one of the major advances of SAT-technology in the last decade.

We describe the basic conflict-analysis algorithm by an example. Assume the database contains the clause  $\{x,y,z\}$  which just became unsatisfied during propagation. This is our conflict. We call  $\overline{x} \wedge \overline{y} \wedge \overline{z}$  the reason set of the conflict. Now x is false because  $\overline{x}$  was propagated from some constraint. We ask that constraint to give us the reason for propagating  $\overline{x}$  (the calcReason() method). It will respond with another conjunction of literals, say  $u \wedge v$ . These were the variable assignment that implied  $\overline{x}$ . The constraint may in fact have been the clause  $\{\overline{u},\overline{v},\overline{x}\}$ . From this little analysis we know that  $u \wedge v \wedge \overline{y} \wedge \overline{z}$  must also lead to a conflict. We may prohibit this conflict by adding the clause  $\{\overline{u},\overline{v},y,z\}$  to the clause database. This would be an example of a learnt conflict clause.

```

class Clause: public Constr

bool

learnt

float

activity

Vec\langle lit \rangle lits

- Constructor - creates a new clause and adds it to watcher lists:

static bool Clause_new(Solver S, Vec\(lit\) ps, bool learnt, Clause out_clause)

"Implementation in Figure 2.8"

- Learnt clauses only:

bool locked(Solver S)

return S.reason[var(lits[0])] == this

- Constraint interface:

void remove(Solver S)

removeElem(this, S.watches[index(\neg lits[0])])

removeElem(this, S.watches[index(\neg lits[1])])

delete this

bool simplify(Solver S)

- only called at top-level with empty prop. queue

int j = 0

for (int i = 0; i < lits.size(); i++)

if (S.value(lits[i]) == TRUE_{\perp})

return True

else if (S.value(lits[i]) == \bot)

lits[j++] = lits[i] - false literals are not copied (only occur for i \ge 2)

lits.shrink(lits.size() - j)

return False

bool propagate(Solver S, lit p)

- Make sure the false literal is lits[1]:

if (lits[0] == \neg p)

lits[0] = lits[1], \, lits[1] = \neg p

- If 0th watch is true, then clause is already satisfied.

if (S.value(lits[0]) == TRUE_{\perp})

S.watches[index(p)].push(this)

- re-insert clause into watcher list

return True

- Look for a new literal to watch:

for (int i = 2; i < size(); i++)

if (S.value(lits[i]) != False_{\perp})

lits[1] = lits[i], lits[i] = \neg p

S.watches[index(\neg lits[1])].push(\mathbf{this})

- insert clause into watcher list

return True

- Clause is unit under assignment:

S.watches[index(p)].push(this)

return S. enqueue(lits[0], this)

- enqueue for propagation

void\ calcReason(Solver\ S,\ lit\ p,\ vec\langle lit\rangle\ out\_reason)

- invariant: (p == \bot) or (p == lits/0)

for (int i = ((p == \bot) ? 0 : 1); i < size(); i++)

out_reason.push(\neg lits[i])

-invariant: S.value(lits/i/) == FALSE_{\perp}

if (learnt) S.claBumpActivity(this)

```

Figure 2.7: Implementation of the *Clause* constraint.

```

bool Clause_new(Solver S, Vec(lit) ps, bool learnt, Clause out_clause)

out\_clause = Null

- Normalize clause:

if (!learnt)

if ("any literal in ps is true")

return True

if ("both p and ¬p occurs in ps") return TRUE

"remove all false literals from ps"

"remove all duplicates from ps"

if (ps.size() == 0)

return False

else if (ps.size() == 1)

return S.enqueue(ps[0])

- unit facts are enqueued

- Allocate clause:

Clause c = new Clause

ps.moveTo(c.lits)

c.learnt = learnt

c.activity = 0

- only relevant for learnt clauses

if (learnt)

- Pick a second literal to watch:

"Let max_i be the index of the literal with highest decision level"

c.lits[1] = ps[max_i], c.lits[max_i] = ps[1]

- Bumping:

S.claBumpActivity(c)

- newly learnt clauses should be considered active

for (int i = 0; i < ps.size(); i++)

S.varBumpActivity(ps[i])

- variables in conflict clauses are bumped

- Add clause to watcher lists:

S.watches[index(\neg c.lits[0])].push(c)

S.watches[index(\neg c.lits[1])].push(c)

out\_clause = c

return True

```

Figure 2.8: Constructor function for clauses. Returns FALSE if top-level conflict is detected. 'out\_clause' may be set to NULL if the new clause is already satisfied under the current top-level assignment. **Post-condition:** 'ps' is cleared. For learnt clauses, all literals will be false except 'lits[0]' (this by design of the analyze() method). For the propagation to work, the second watch must be put on the literal which will first be unbound by backtracking. (Note that none of the learnt-clause specific things needs to be done for a user defined constraint type.)

```

Constr Solver.propagate()

while (propQ.size() > 0)

- 'p' is now the enqueued fact to propagate

lit p = propQ.dequeue()

Vec \langle Constr \rangle tmp

- 'tmp' will contain the watcher list for 'p'

watches[index(p)].moveTo(tmp)

for (int i = 0; i < tmp.size(); i++)

if (!tmp[i].propagate(this, p))

- Constraint is conflicting; copy remaining watches to 'watches[p]'

- and return constraint:

for (int j = i+1; j < tmp.size(); j++)

watches[index(p)].push(tmp[j])

propQ.clear()

return tmp[i]

return Null

bool Solver.enqueue(lit p, Constr from = Null)

if (value(p) != \bot)

if (value(p) == FALSE_{\perp})

- Conflicting enqueued assignment

return False

else

- Existing consistent assignment - don't enqueue

return True

else

New fact, store it

assigns [var(p)] = lbool(!sign(p))

[var(p)] = decisionLevel()

```

Figure 2.9: **propagate()**: Propagates all enqueued facts. If a conflict arises, the *conflicting* clause is returned, otherwise NULL. **enqueue()**: Puts a new fact on the propagation queue, as well as immediately updating the variable's value in the assignment vector. If a conflict arises, FALSE is returned and the propagation queue is cleared. The parameter 'from' contains a reference to the constraint from which 'p' was propagated (defaults to NULL if omitted).

reason [var(p)] = from

trail.push(p) propQ.insert(p) return True

In the example, we picked only one literal and analyzed it one step. The process of expanding literals with their reason sets can be continued, in the extreme case until all the literals of the conflict set are decision variables (which were not propagated by any constraints). Different learning schemes based on this process have been proposed. Experimentally the "First Unique Implication Point" (First UIP) heuristic has been shown effective [ZMMM01]. We will not give the definition of UIPs here, but just state the algorithm: In a breadth-first manner, continue to expand literals of the current decision level, until there is just one left.

In the code for analyze(), displayed in Figure 2.10, we make use of the fact that a breadth-first traversal can be achieved by inspecting the trail backwards. Especially, the variables of the reason set of p is always before p in the trail. Fur-

thermore, in the algorithm we initialize p to  $\perp_{lit}$ , which will make calcReason() return the reason for the conflict.

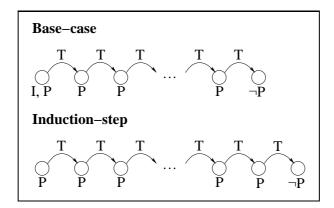

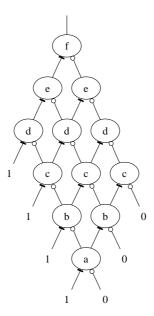

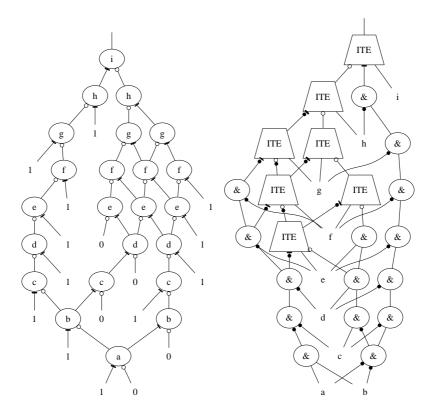

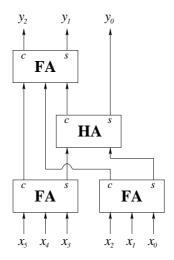

Assuming x to be the unit information that causes the conflict, an alternative implementation would be to calculate the reason for  $\overline{x}$  and just add x to that set. The code would be slightly more cumbersome but the contract for calcReason() would be simpler, as we no longer need the special case for  $\bot_{lit}$ .